#### **Features**

- Wide Operating Voltage Range of 2 V to 6V

- Outputs Can Drive Up To 10 LSTTL Loads

- Low Power Consumption, 80- µ A Max I<sub>CC</sub>

- Typical t<sub>pd</sub> =20 ns

- ± 4-mA Output Drive at 5V

- Low Input Current of 1µ A Max

- AND-Gated (Enable/Disable) Serial Inputs

- Fully Buffered Clock and Serial Inputs

- Direct Clear

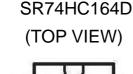

#### **Description/ordering information**

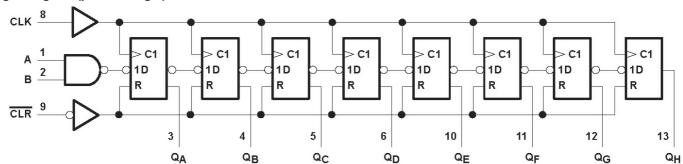

These 8-bit shift registers feature AND-gated serial inputs and an asynchronous clear (CLR) input. The gated serial (A and B) input permit complete control over incoming data; a low at either input inhibits entry of the new data and resets the first flip-flop to the low level at the next clock (CLK) pulse. A high-level input enables the other input, which then determines the state of the first flip-flop. Data at the serial inputs can be changed while CLK is high or low, provided the minimum setup time requirements are met. Clocking occurs on the low-to-high-level transition of CLK.

SR74HC164D (3D VIEW)

## **ORDERING INFORMATION**

| T <sub>A</sub> | PAC      | PACKAGE† ORDERABLE |            |           |  |  |

|----------------|----------|--------------------|------------|-----------|--|--|

| ·              |          |                    | PARTNUMBER | MARKING   |  |  |

| -40 to 85      | SOIC - D | Reel of 2500       | SR74HC164D | SR74HC164 |  |  |

Page: 1/7

#### **FUNCTION TABLE**

|     | INP        | UTS | OUTPUTS |                 |                                    |  |

|-----|------------|-----|---------|-----------------|------------------------------------|--|

| CLR | CLK        | Α   | В       | QA              |                                    |  |

| L   | Х          | Х   | Х       | L               | L L                                |  |

| н   | L          | X   | X       | Q <sub>AO</sub> | Q <sub>BO</sub> Q <sub>HO</sub>    |  |

| Н   | $\uparrow$ | Н   | Н       | Н               | $Q_{An}  Q_{Gn}$                   |  |

| Н   | $\uparrow$ | L   | X       | L               | $\mathbf{Q}_{An}  \mathbf{Q}_{Gn}$ |  |

| Н   | <b>↑</b>   | X   | L       | L               | $Q_{An}  Q_{Gn}$                   |  |

$Q_{A0}$ ,  $Q_{B0}$ ,  $Q_{H0}$  = the level of  $Q_A$ ,  $Q_B$ , or  $Q_H$ , respectively, before the indicated steady-state input conditions were established

$Q_{An}$ ,  $Q_{Gn}$  = the level of  $Q_A$  or  $Q_G$  before the most recent  $\uparrow$  transition of CLK: indicates a 1-bit shift

# logic diagram (positive logic)

Pin numbers shown are for the D packages.

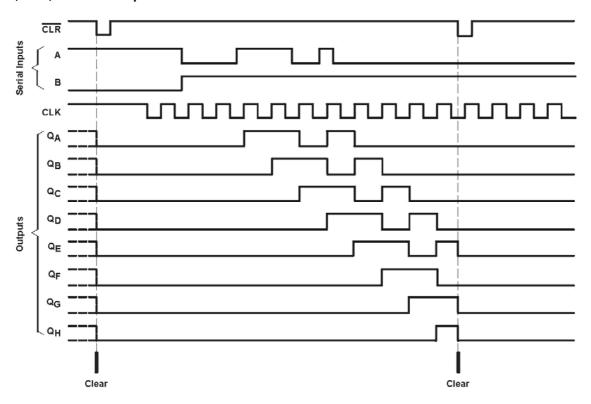

#### Typical clear, shift, and clear sequence

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted) †

| Supply voltage range, V <sub>CC</sub> 0.                                                                     | 5 V to  | 7 V |

|--------------------------------------------------------------------------------------------------------------|---------|-----|

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0 or V <sub>I</sub> >V <sub>CC</sub> ) (see Note 1)   | . ± 20r | mΑ  |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) (see Note 1) | ± 20r   | mΑ  |

| Continuous output current, $I_0$ ( $V_0 = 0$ to $V_{CC}$ )                                                   | ± 25    | mΑ  |

| Continuous current through V <sub>CC</sub> or GND                                                            | ± 50ı   | mΑ  |

| Package thermal impedance, $\theta_{JA}$ (see Note 2): D package                                             | 86      | /W  |

| Storage temperature range, T stg65                                                                           | to 15   | 0   |

†Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

2. The package thermal impedance is calculated in accordance with JESD 51-7

## Recommended operating conditions (see Note 3)

|                  |                                 |                       | SR7  | '4HC164I | D    | LINUT |

|------------------|---------------------------------|-----------------------|------|----------|------|-------|

|                  |                                 |                       | MIN  | NOM      | MAX  | UNIT  |

| V <sub>C</sub> C | Supply voltage                  |                       | 2    | 5        | 6    | V     |

|                  |                                 | V <sub>CC</sub> =2V   | 1.5  |          |      |       |

| V <sub>IH</sub>  | High-level input voltage        | V <sub>CC</sub> =4.5V | 3.15 |          |      | V     |

|                  |                                 | V <sub>CC</sub> =6V   | 4.2  |          |      |       |

|                  |                                 | V <sub>CC</sub> =2V   |      |          | 0.5  |       |

| V <sub>IL</sub>  | Low-level input voltage         | V <sub>CC</sub> =4.5V |      |          | 1.35 | V     |

|                  |                                 | V <sub>CC</sub> =6V   |      |          | 1.8  |       |

| VI               | Input voltage                   |                       | 0    |          | Vcc  | V     |

| Vo               | Output voltage                  |                       | 0    |          | Vcc  | V     |

|                  |                                 | V <sub>CC</sub> =2V   |      |          | 1000 |       |

| t / v†           | Input transition rise/fall time | V <sub>CC</sub> =4.5V |      |          | 500  | ns    |

|                  |                                 | V <sub>CC</sub> =6V   |      |          | 400  |       |

| TA               | Operating free-air temperature  |                       | -40  |          | 85   |       |

NOTE 3: All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report. Implications of Slow or Floating CMOS Inputs, literature number SCBAOO4.

#### Electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| DADAMETED       | TEST CONDITIONS                                      |                           | VCC      | $T_A = 25$ |       |       | SR74HC164D |                          | LINIT |     |      |      |  |      |

|-----------------|------------------------------------------------------|---------------------------|----------|------------|-------|-------|------------|--------------------------|-------|-----|------|------|--|------|

| PARAMETER       |                                                      |                           | VCC      | MIN        | TYP   | MAX   | MII        | I MAX                    | UNIT  |     |      |      |  |      |

|                 |                                                      |                           | 2V       | 1.9        | 1.998 |       | 1.         | 9                        |       |     |      |      |  |      |

|                 |                                                      | I <sub>OH</sub> = -20 μ A | 4.5V     | 4.4        | 4.499 |       | 4.         | 4                        |       |     |      |      |  |      |

| V <sub>OH</sub> | V <sub>I</sub> = V <sub>IH</sub> or V <sub>I</sub> L |                           | 6V       | 5.9        | 5.999 |       | 5.         | 9                        | V     |     |      |      |  |      |

|                 |                                                      | $I_{OH} = -4mA$           | 4.5V     | 3.98       | 4.3   |       | 3.8        | 4                        |       |     |      |      |  |      |

|                 |                                                      | $I_{OH} = -5.2 \text{mA}$ | 6V       | 5.48       | 5.8   |       | 5.3        | 4                        |       |     |      |      |  |      |

|                 | V <sub>I</sub> = V <sub>IH</sub> or V <sub>I</sub> L |                           |          |            | 2V    |       | 0.002      | 0.1                      |       | 0.1 |      |      |  |      |

|                 |                                                      | I <sub>OL</sub> = 20 μ A  | 4.5V     |            | 0.001 | 0.1   |            | 0.1                      |       |     |      |      |  |      |

| V <sub>OL</sub> |                                                      |                           | 6V       |            | 0.001 | 0.1   |            | 0.1                      | V     |     |      |      |  |      |

|                 |                                                      | $I_{OL} = 4mA$            | 4.5V     |            | 0.17  | 0.26  |            | 0.33                     |       |     |      |      |  |      |

|                 |                                                      |                           |          |            |       |       |            | $I_{OH} = 5.2 \text{mA}$ | 6V    |     | 0.15 | 0.26 |  | 0.33 |

| II              | $V_I = V_{CC}$ or 0                                  |                           | 6V       |            | ± 0.1 | ± 100 |            | ±1000                    | nA    |     |      |      |  |      |

| Icc             | $V_I = V_{CC}$ or 0,                                 | I <sub>O</sub> =0         | 6V       |            |       | 8     |            | 80                       | μΑ    |     |      |      |  |      |

| C <sub>i</sub>  | -                                                    | ·                         | 2V to 6V |            | 3     | 10    |            | 10                       | pF    |     |      |      |  |      |

<sup>†</sup> If this device is used in the threshold region (from  $V_{IL}$  max = 0.5V to  $V_{IH}$  min =1.5V), there is a potential to go into the wrong state from induced grounding, causing double clocking. Operating with the inputs at t<sub>t</sub> =1000ns and  $V_{CC}$  = 2V does not damage the device; however, functionally, the CLK inputs are not ensured while in the shift, count, or toggle operating modes.

Timing requirements over recommended operating free-air temperature range (unless otherwise noted)

|                 |                           |                     | V    | T <sub>A</sub> = | =25 | SR74HC | 164D | LINUT |

|-----------------|---------------------------|---------------------|------|------------------|-----|--------|------|-------|

|                 |                           |                     | VCC  | MIN              | MAX | MIN    | MAX  | UNIT  |

|                 |                           |                     | 2V   |                  | 6   |        | 5    |       |

| f clock         | Clock frequency           |                     | 4.5V |                  | 31  |        | 25   | MHz   |

|                 |                           |                     | 6V   |                  | 36  |        | 28   |       |

|                 |                           |                     | 2V   | 100              |     | 125    |      |       |

|                 |                           | CLR low             | 4.5V | 20               |     | 25     |      |       |

| 4               | Dulas duration            |                     | 6V   | 17               |     | 21     |      | ns    |

| t w             | Pulse duration            | CLK high or low     | 2V   | 80               |     | 100    |      |       |

|                 |                           |                     | 4.5V | 16               |     | 20     |      |       |

|                 |                           |                     | 6V   | 14               |     | 18     |      |       |

|                 |                           | Data                | 2V   | 100              |     | 125    |      | ns    |

|                 |                           |                     | 4.5V | 20               |     | 25     |      |       |

| 4               | Catua tima hafara CLICA   |                     | 6V   | 17               |     | 21     |      |       |

| t <sub>su</sub> | Setup time before CLK↑    |                     | 2V   | 100              |     | 125    |      |       |

|                 |                           | <b>CLR</b> inactive | 4.5V | 20               |     | 25     |      |       |

|                 |                           |                     | 6V   | 17               |     | 21     |      |       |

|                 |                           |                     | 2V   | 5                |     | 5      |      | ns    |

| t h             | Hold time, data after CLK | (↑                  | 4.5V | 5                |     | 5      |      |       |

|                 |                           |                     | 6V   | 5                |     | 5      |      |       |

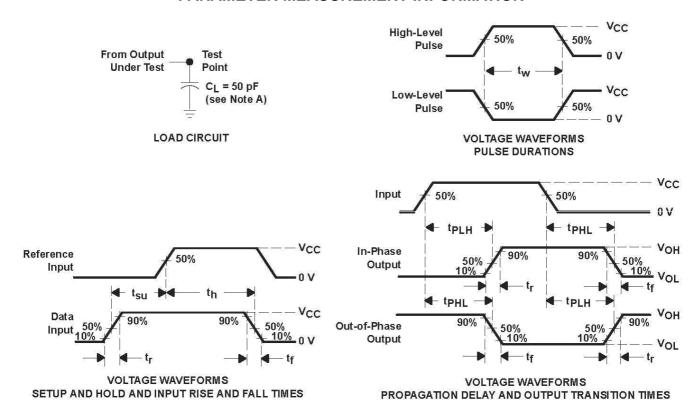

Switching characteristics over recommended operating free-air temperature range, CL = 50pF (unless otherwise noted) (see Figure1)

| PARAMETER        | FROM    | ТО       | V    |     | T <sub>A</sub> =25 | j   | SR74H | C164D | UNIT |

|------------------|---------|----------|------|-----|--------------------|-----|-------|-------|------|

| PARAMETER        | (INPUT) | (OUTPUT) | Vcc  | MIN | TYP                | MAX | MIN   | MAX   | UNIT |

|                  |         |          | 2V   | 6   | 10                 |     | 5     |       |      |

| f <sub>max</sub> |         |          | 4.5V | 31  | 54                 |     | 25    |       | MHz  |

|                  |         |          | 6V   | 36  | 62                 |     | 28    |       |      |

|                  |         |          | 2V   |     | 140                | 205 |       | 255   |      |

| t PHL            | CLR     | Any Q    | 4.5V |     | 28                 | 41  |       | 51    |      |

|                  |         |          | 6V   |     | 24                 | 35  |       | 46    | Ns   |

|                  |         |          | 2V   |     | 115                | 175 |       | 220   | INS  |

| t <sub>pd</sub>  | CLK     | Any Q    | 4.5V |     | 23                 | 35  |       | 44    |      |

|                  |         |          | 6V   |     | 20                 | 30  |       | 38    |      |

|                  |         |          | 2V   |     | 38                 | 75  |       | 95    |      |

| t t              |         |          | 4.5V |     | 8                  | 15  |       | 19    | ns   |

|                  |         |          | 6V   |     | 6                  | 13  |       | 16    |      |

# Operating characteristics, $T_A = 25$

|                 | PARAMETER                     | TESTCONDITIONS | TYP | UNIT |

|-----------------|-------------------------------|----------------|-----|------|

| C <sub>pd</sub> | Power dissipation capacitance | No load        | 135 | pF   |

### PARAMETER MEASUREMENT INFORMATION

**NOTES:** A. C<sub>L</sub> includes probe and test-fixture capacitance.

- B. Phase relation ships between waveforms were chosen arbitrarily. All input pulses are supplied by generators having the following characteristics: PRR  $\,$  1MHz,  $Z_O = 50$   $\,$ ,  $t_r = 6$ ns,  $t_f = 6$ ns.

- C. For clock inputs,  $f_{max}$  is measured when the input duty cycle is 50%.

- D. The outputs are measured one at a time with one input transition per measurement.

- E.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pd}$ .

Figure 1. Load Circuit and Voltage Waveforms

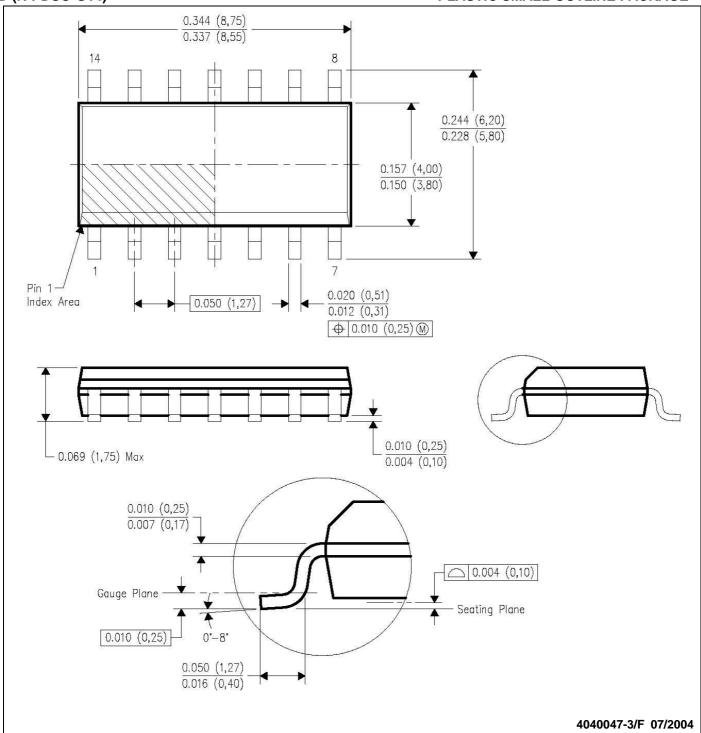

## **MECHANICAL DATA**

## D (R-PDSO-G14)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0.15).

- D. Falls within JEDEC MS-012 variation AB.